#### **About Me**

- Ryan Junee BE (Hons I) BCom

- Research Engineer @ Sensory Networks

- Graduate of Sydney University

- Teach a variety of subjects at Sydney Uni

- currently head tutor of ELEC5610 Computer and Network Security

ryan@junee.org http://ryan.junee.org

#### **About Me**

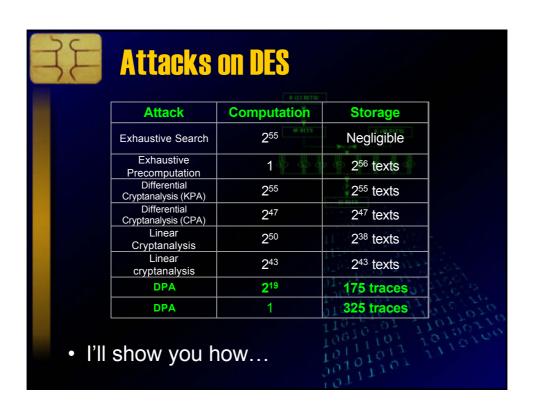

- 2002 Thesis: "Power Analysis Attacks :: A Weakness in Cryptographic Smart Cards and Microprocessors"

- Successfully recovered DES secret key using Differential Power Analysis (DPA)

- Featured on the front page of Australian IT

#### **About Smart Cards**

- Growing use in a wide range of industries worldwide:

- SMARTICS identity card for citizens of Hong Kong. Stores ID & 3<sup>rd</sup> party info.

- Drivers licenses in the Philippines record name, address, fingerprint, photo, offences...

- Transport ticketing in Washington (1/3 of WMATA Metrorail riders use SmarTrip cards)

- Pay television, health care, ...

### **About Smart Cards**

- Recent headlines:

- "NSW announces smart card fare system"

- "First Gas Pumps Accept MasterCard® PayPass"

- "Mexico Moves To Smart Tax Payment System"

- "Terrorist attacks spark military smart cards"

- "MasterCard Records 65 Percent Growth in Smart Card Issuance in Asia/Pacific"

- Has anyone considered the risks??

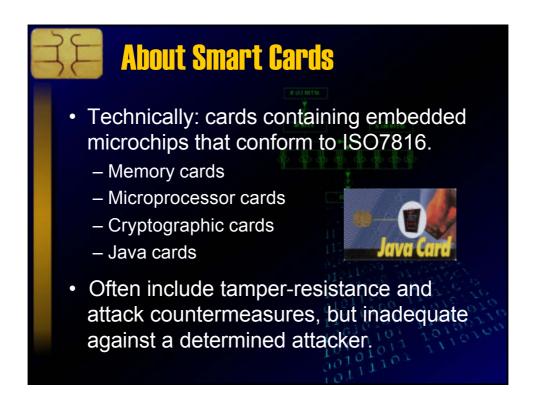

# **About Smart Cards**

- Smart cards are gaining popularity in applications that require high security and/or store sensitive information.

- Traditionally seen as secure and tamper resistant (especially compared to magnetic stripe cards).

- We are not there yet...

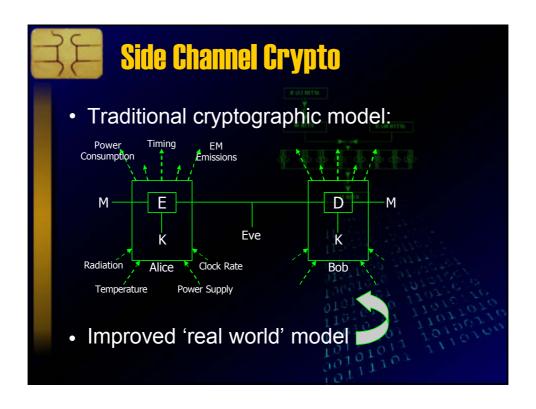

#### **Timing Attacks**

- Cryptosystems can take different amounts of time to process different inputs.

- Performance optimisations in software

- Branching/conditional statements

- Caching in RAM

- Variable length instructions (multiply, divide)

- Simply take accurate timing measurements with various input data to deduce internal workings.

### **Timing Attacks**

- Simple example Naive password checking function.

- Interesting paradox: As computers become faster and networks have less latency, timing measurements become more accurate!

- Future research: a timing attack on SSH exploiting keystroke timing statistics?

#### **Timing Attacks**

- Countermeasures

- Make all operations run in same amount of time

- · Can't design platform-independent algorithms

- All operations take as long as slowest one

- Add random delays

- · Can take more samples to remove randomness

- Blind signature techniques

- · Algorithm specific

# **Fault Analysis**

- Single innocent faults can have large security implications.

- Faults can be induced.

- Simple example: bit controls ciphertext or plaintext output.

- Flip bit with power surge, radiation, laser etc

- Engineering criteria (e.g. FIPS140-1) generally prevent such simple attacks.

### **Fault Analysis**

- Differential Fault Analysis

- Biham, Shamir 1997

- Intrusive Fault Analysis

- E.g. damaging registers in the last round of a DES operation can reveal S-box input and hence round key.

# **Fault Analysis**

- Countermeasures

- Verify correctness of output before transmitting it to outside world

- Can increase work by a factor of 2

- · Fault could also occur in verification

- Make devices tamper resistant (strong shielding, detect supply voltages and clock speeds)

- · Costly, increase device footprint

#### **Power Analysis**

- Logic gates made from transistors draw current when switching states

- Power consumed depends on:

- opcode, operand data, contents of registers, buses and memory, previous instructions (pipeline)

- Measure current by placing a resistor in series with supply or ground pin

### **Power Analysis**

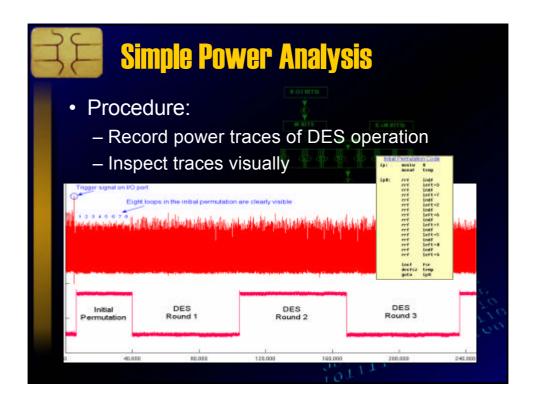

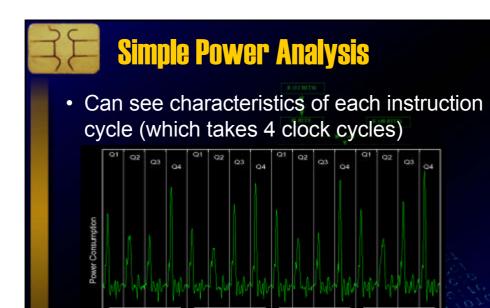

- Simple Power Analysis

- Can observe macro characteristics of underlying algorithm (loops, conditionals etc)

- Differential Power Analysis

- Use statistical techniques to reveal much smaller power variations

- Inferential Power Analysis

- Profile hardware. Subsequent attacks require as little as one trace!

- More detail on SPA/DPA in Part II

#### **Power Analysis**

- Countermeasures

- Don't use secret values in conditionals/loops

- · May mean code has sub-optimal performance

- Ensure little variation in power consumption between instructions

- · Requires consideration of low level logic design

- More discussed at the end

### **EM Emissions**

- Large body of classified literature.

Recently being realised in public domain research

- Direct emanations caused by current flows in circuit

- Unintentional emanations caused by electrical/electromagnetic coupling between components in close proximity

## **EM Emissions**

- 2002 paper from IBM shows different signals present in different parts of spectrum

- Some can be detected with antennas from a distance. Best results if chip is decapsulated from packaging

- Contain more information than power leakage, resistant to countermeasures.

- · Watch this space!

### **EM Emissions**

- Countermeasures

- Redesign circuits to prevent unintentional emissions

- Costly

- Shielding

- · Costly, increase device footprint

- Introduce EM noise

- · Can be averaged out

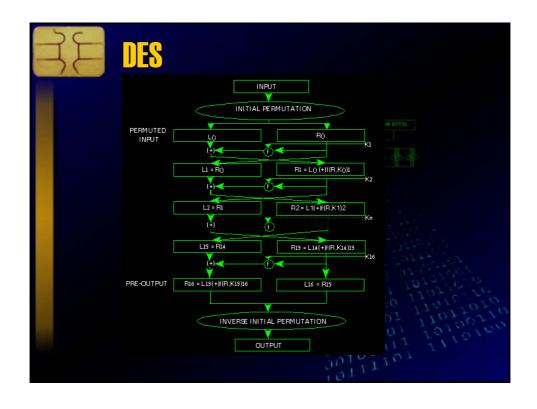

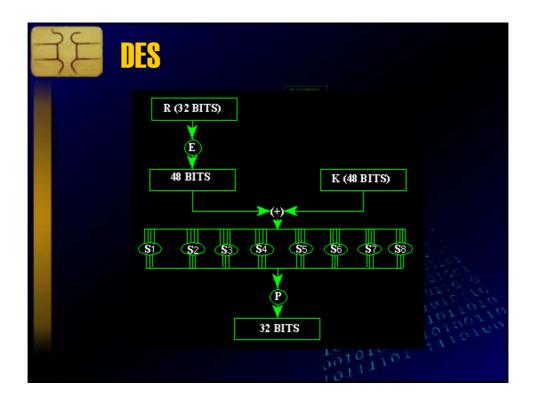

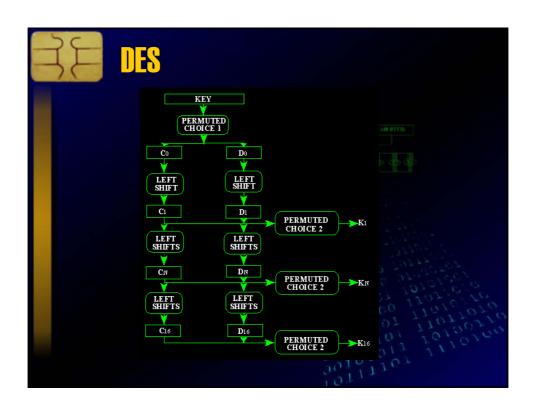

# **Differential Power Analysis**

- Perform approx 400 DES encryptions with arbitrary plaintext. Record the resulting power trace and ciphertext output.

- Brute force a particular 6-bit subkey from DES round 16

- For each guess, calculate the value of a particular bit in L15 corresponding to the subkey (there are 4 such bits)

- Partition the traces into two sets, one where the 'select bit' is 0, one where it is 1.

### **Differential Power Analysis**

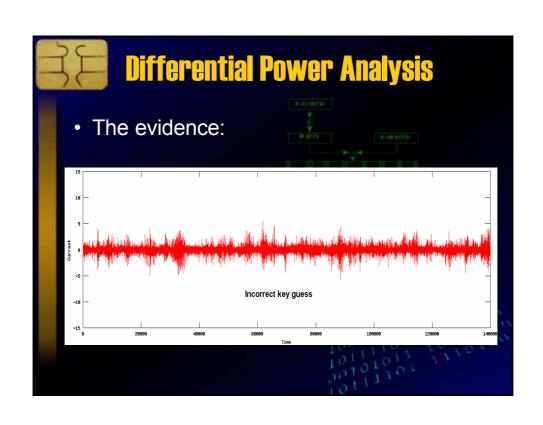

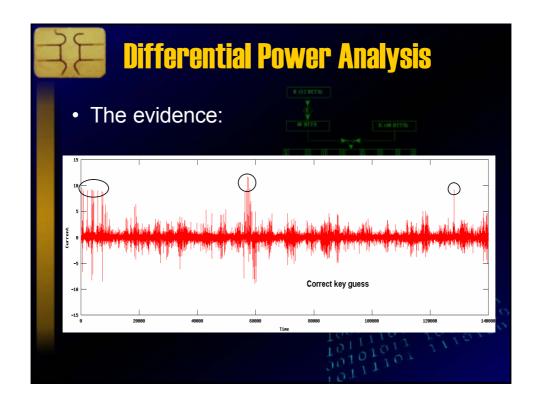

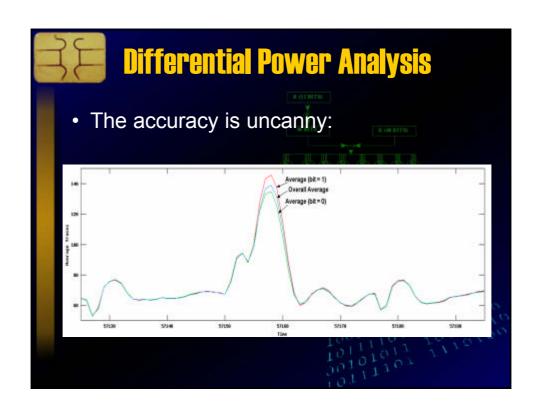

- Calculate the average power trace for each set, then subtract to <u>form differential trace</u>.

- Assume correlation between power consumed and value of select bit

- (it is manipulated somewhere in the power trace)

- If key guess was correct => peaks in the differential trace

- If not we have made a random partition => differential trace should approach zero.

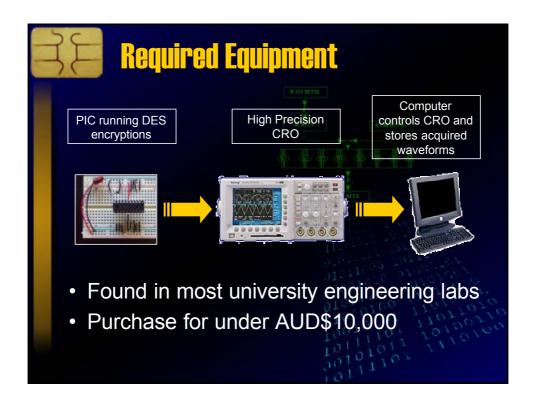

#### **Differential Power Analysis**

- The low down:

- 400 traces acquired (approx. 22 hours)

- 1.6 hours computation (Celeron 400MHz)

- DES key cracked!

- Brute force key search on same computer would take 57 thousand years!

- Code is available on my web site (you will need access to a CRO etc)

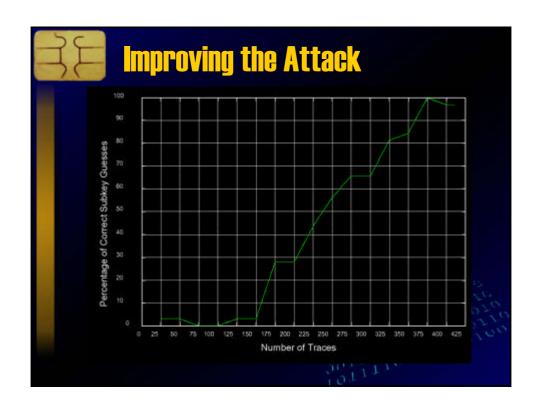

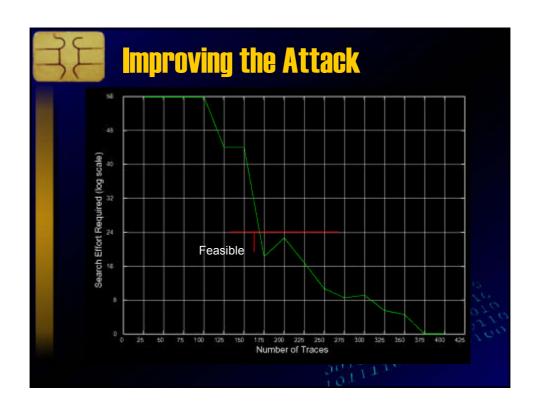

### **Improving the Attack**

- Improvement 1 Reduce acquisition time

- Bottleneck is 38400 baud serial transfer

- Use ethernet or GPIB

- Lower sampling rate (currently 50/cycle)

- Improvement 2 Reduce computation time

- Use faster CPU

- Parallel computation

- Improvement 3 Reduce number of traces required

#### **Future work**

- As observed, uncanny accuracy in power traces

- Power trace disassembler:

- Profile all instructions

- Use statistical methods or AI to disassemble the execution trace of an algorithm by observing power consumption

- Reverse engineering tool?

### **Power Analysis Countermeasures**

- Countermeasures

- Reducing power variations (shielding, balancing)

- Randomness (power, execution, timing) + counters on card

- Algorithm redesign (non-linear key update, blinding)

- Hardware redesign (decouple power supply, gatelevel design)

- 2002: Kocher released automated DPA cracker.

Sell to approved researchers/manufacturers

- Suspect not many cards employ adequate countermeasures